题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[单选题]

3 线-8 线二进制译码器工作时,任一时刻译码器输出端的有效电平的个数是()。

A.4

B.1

C.16

D.24

答案

答案

查看答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.4

B.1

C.16

D.24

答案

答案

更多“3 线-8 线二进制译码器工作时,任一时刻译码器输出端的有效电平的个数是()。”相关的问题

更多“3 线-8 线二进制译码器工作时,任一时刻译码器输出端的有效电平的个数是()。”相关的问题

第1题

试用3线-8线译码器和8线-3线优先编码器构成y=(3x)mod8电路,x和y都是三位二进制数。8线-3线优先编码器的逻辑符号如图所示。

第2题

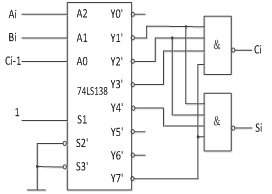

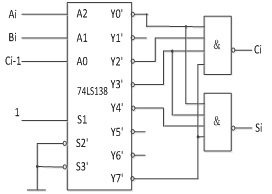

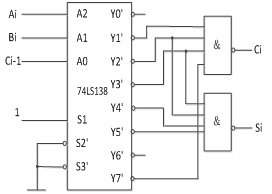

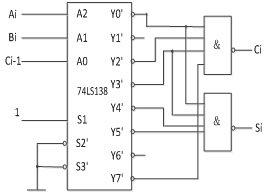

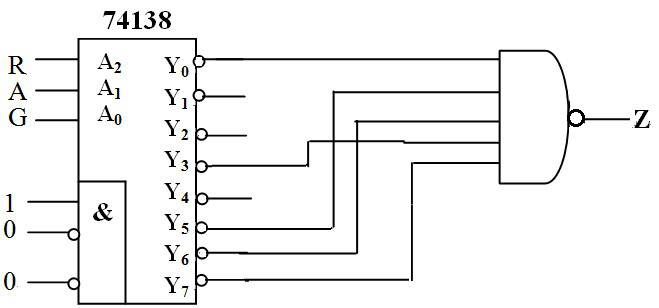

用3线—8线译码器设计一个既能做一位二进制数的令加运算,又能做一位二进制数的伞减运算的电路。

要求:(1)根据题意要求,写真值表。

(2)写出电路输出函数的最简与或表达式。

(3)画出用3线—8线译码器74LS138芯片实现的电路。

第3题

试用输出低电平有效的3线-8线译码器和逻辑门设计一组合电路。该电路输入X,输出F均为3位二进制数。二者之间关系如下:

2≤X≤5时,F=X+2

X<2时,F=1

X>5时,F=0

第4题

A.

B.

C.

D.

第5题

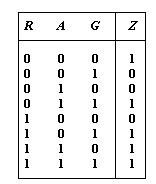

A、真值表:

B、真值表:

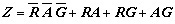

C、逻辑函数表达式:

D、利用与非门设计实现:

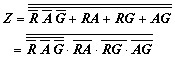

E、利用3线-8线译码器芯片74138及基本逻辑门设计实现:

第6题

设计一个组合逻辑电路,当M=1时,两个2位二进制数A=A1A0和B=B180实现全加;当M=0时,两个二进制数实现全减。要求用两片3线-8线译码器74HC138实现,必要时可用门电路。

第7题

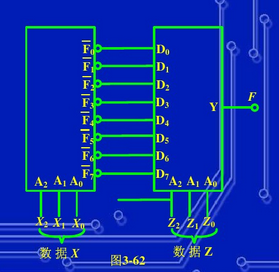

由输出低电平有效的3线-8线译码器和8选1数据选择器构成的电路如图4-20所示,

(1)X2X1X0=Z2Z1Z0时,求输出F;

(2)X2X1X0≠Z2Z1Z0时,求输出F。