题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

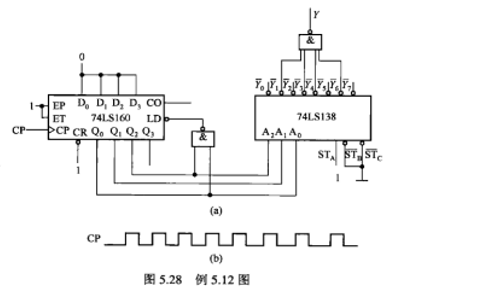

图(a)所示电路为同步十进制加法计数器74160和3线-8线译码器74138组成的电路,74138输出低电平有效,使能端。

图(a)所示电路为同步十进制加法计数器74160和3线-8线译码器74138组成的电路,74138输出低电平有效,使能端

答案

答案

查看答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

图(a)所示电路为同步十进制加法计数器74160和3线-8线译码器74138组成的电路,74138输出低电平有效,使能端

答案

答案

更多“图(a)所示电路为同步十进制加法计数器74160和3线-8线译码器74138组成的电路,74138输出低电平有效,使能端。”相关的问题

更多“图(a)所示电路为同步十进制加法计数器74160和3线-8线译码器74138组成的电路,74138输出低电平有效,使能端。”相关的问题

第1题

有效,使能端处于有效状态.

(1)74160构成多少进制计数器.

(2)假定74160初始状态Q3Q2Q1Q0=0000,试对应图5.28(b)的CP脉冲图画出Q3、Q2、Q1、Q0和Y的输出波形.

第5题

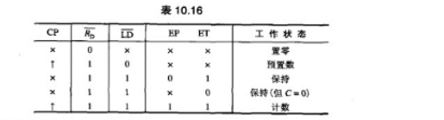

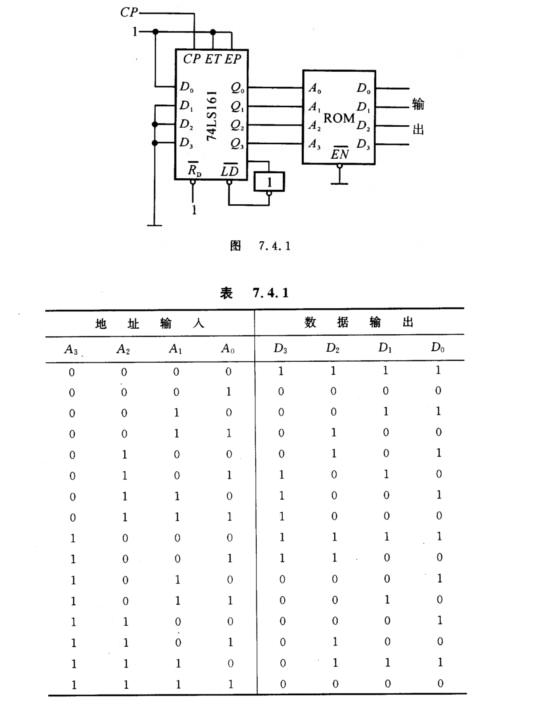

试分析图11.20(a)电路的工作原理,画出输出电压vO的波形图。其中,74HC151是8选1数据选择器。74LS161为同步十六进制加法计数器。假定74LS161和反相器G1的输出电阻远远小于R的阻值。74HC151各输入端的电压波形如图11.20(b)所示。

第6题

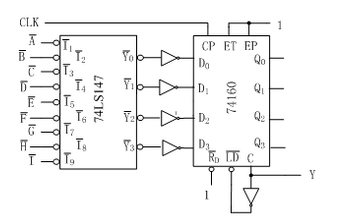

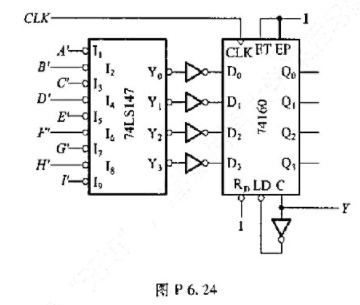

制信号A、B、C、D、E、F、G、H、I分别为低电平时由Y端输出的脉冲频率各为多少?已知CLK端的输入脉冲频率为10kHz。

第7题

第8题

第9题

第10题

图4-63所示为由二一十进制编码器74147和同步十进制计数器74162组成的可控分频器。试说明输入信号A、B、C、D、E、F、G、H、J分别为低电平时,由f端输出的信号频率依次为多少。假设CP的重复频率为10kHz。

.jpg)