题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

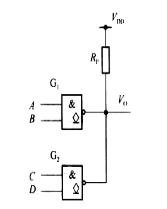

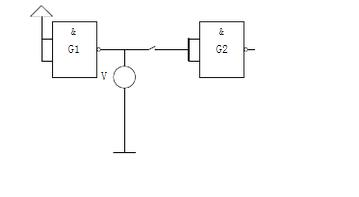

在图P3.5电路中,已知OD门G1、G2输出高电平时输出端MOS管的漏电流为IOH(max)=5μA;输出电流为IOL(max)=10mA时,

在图P3.5电路中,已知OD门G1、G2输出高电平时输出端MOS管的漏电流为IOH(max)=5μA;输出电流为IOL(max)=10mA时,输出低电平为VOL≤0.3V。若取VDD=5V,试计算在保证VOH≥3.5V、VOL≤0.3V的条件下,外接电阻RP,取值的允许范围。

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

在图P3.5电路中,已知OD门G1、G2输出高电平时输出端MOS管的漏电流为IOH(max)=5μA;输出电流为IOL(max)=10mA时,输出低电平为VOL≤0.3V。若取VDD=5V,试计算在保证VOH≥3.5V、VOL≤0.3V的条件下,外接电阻RP,取值的允许范围。

答案

答案

更多“在图P3.5电路中,已知OD门G1、G2输出高电平时输出端MOS管的漏电流为IOH(max)=5μA;输出电流为IOL(max)=10mA时,”相关的问题

更多“在图P3.5电路中,已知OD门G1、G2输出高电平时输出端MOS管的漏电流为IOH(max)=5μA;输出电流为IOL(max)=10mA时,”相关的问题

第1题

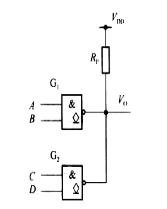

在图题6.2(a)所示的施密特触发器电路中,已知R1=10kΩ,R2=30kΩ,G1和G2为CMOS反相器,VDD=15V。

(1) 试计算电路的正向阈值电压VT+、负向阈值电压VT-和回差电压△VT。

(2) 若将图题6.2(b)给出的电压信号加到图题6.2(a)电路的输入端,试画出电压的波形。

第2题

在图9.3.1(a)所示的施密特触发器电路中,已知R1=10 kΩ,R2=30 kΩ。G1和G2为CM()S反相器,VDD=15 V。 (1)试计算电路的上限触发电平VT+,下限触发电平VT-和回差电压△VT. (2)若将图9.3.1(b)给出的电压信号加到图9.3.1(a)电路的输出端,试画出输出电压的波形。

1.jpg)

第3题

图P3.6是用输出端并联的OD门驱动CMOS反相器和与非门的电路。试计算当VDD=5V时外接电阻RP阻值的合理范围。要求OD门输出的高、低电平满足VOH≥3.5V、VOL≤0.3V。已知OD门G1~G3输出高电平时,每个输出端MOS管的漏电流为IOH(max)=10μA;输出低电平时,每个输出端MOS管输出电流的最大值为IOL(max)=4mA,输出低电平VOL≤0.3V。CMOS反相器和与非门每个输入端的高电平输入电流和低电平输入电流最大值均为1μA。

第4题

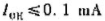

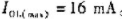

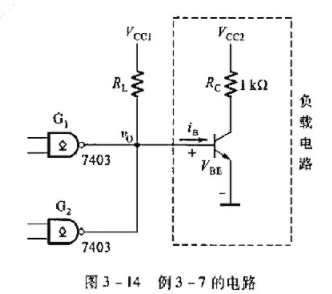

已知OC门7403输出高电平时输出端三极管的蒲电流为 ,输出为低电平

,输出为低电平 时允许流入的最大负载电流为

时允许流入的最大负载电流为 三极管T的电流放大系数β=50,集电极负载电阻

三极管T的电流放大系数β=50,集电极负载电阻 饱和导通压降

饱和导通压降 0.1V.饱和导通内阻

0.1V.饱和导通内阻 .给定

.给定 试求R取值的允许范围.

试求R取值的允许范围.

第5题

D(max)

=1mA,IIH(max)=40uA,试分析G1门输出高、低电平两种情况下电路能否正常工作.

第6题

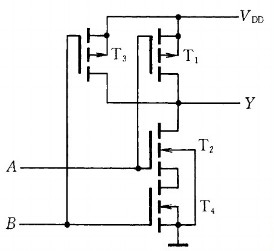

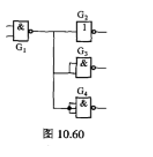

图2.3.5所示电路中,(a)图中的G1、G2均为CMOS门电路;(b)图中G1、G2和G3均为TTL门电路,G4为CMOS门电路。试写出Y1和Y2的逻辑表达式。

第7题

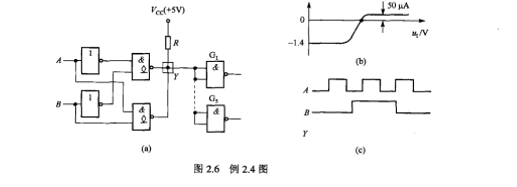

过的最大负载电流ILM≤15mA,输出Y的高、低电平满足UOH≥3V,UOL≤0.4V与非门G1~G5的输入特性如图2.6(b)所示,输入A、B的波形如图2.6(c)所示.

(1)写出函数Y的逻辑表达式.

(2)画出输出Y与输入A、B的对应波形.

(3)计算电阻R的取值范围.

第8题

电路如图2.2.6所示。图中,G1为三态门,G2为TTL门。E控制端为低电平选通,试分别求出E为低电平及高电平两种情况下,开关S在闭合及断开两种状态下的电压表的测量值为多少?(设电压表内阻为20kQ)

第9题

试计算图3.6.2(a)所示电路中门G最多可以驱动多少个负载门。已知G0和负载门G1,…,Gn均为LSTTL与非门,它们的输入特性和输出特性由图3.6.2(b),(c),(d)给出。由于功耗的限制,规定高电平输出电流不能超过400μA。要求门G0的输出电平满足VOH≥3.2 V,VOL≤0.25 V。

第10题

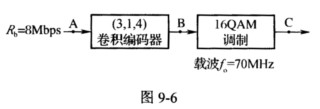

取值1、0的二进制独立等概序列经(3,1,4)卷积编码(卷积编码器的约束长度K=4,移位寄存器级数为m=K-4=3)后,送至16QAM数字调制器,如图9-6所示。已知此卷积码的生成多项式是g1(x)=1,g2(x)=l+x2+x3, g3(x)=l+x+x2+x3。 (1)画出卷积码编码器电路; (2)求出图9-6中B、C处的码元速率,画出C点的功率谱密度图;

(3)画出16QAM的信号空间图,并求出星座图中最小的欧式距离平方和平均能量之比(假设采用常规矩形星座,各星座点等概出现)。

(3)画出16QAM的信号空间图,并求出星座图中最小的欧式距离平方和平均能量之比(假设采用常规矩形星座,各星座点等概出现)。