题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

设有一个四体低位交叉的存储器,每个体的容量为256K×64位,存取周期为200 ns。则数据总线的宽度为__

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

更多“设有一个四体低位交叉的存储器,每个体的容量为256K×64位,存取周期为200 ns。则数据总线的宽度为__”相关的问题

更多“设有一个四体低位交叉的存储器,每个体的容量为256K×64位,存取周期为200 ns。则数据总线的宽度为__”相关的问题

第1题

A.在0.1 μs内,存储器可向CPU提供26位二进制信息

B.在0.1 μs内,每个体可向CPU提供16位二进制信息

C.在0.4 μs内,存储器可向CPU提供26位二进制信息

第2题

设n体交叉编址(低位交叉)存储器中每个体的存储字长等于数据总线宽度,每个体存取一个字的存取周期为T,总线传输周期为t,T与t的关系以及读取地址连续的n个字需要的时间分别是()。

A. T=t,T+n×t

B. T=(n一1)×t,T+n×t

C.T=n×t,T+n×t

D. T=n×t,T+(n一1)×t

第3题

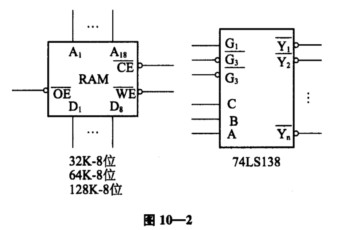

设CPU有18根地址线和8根数据线,并用IO/M(M取反)作访存控制信号,R/W(W取反)作读写命令,存储器采用四体低位交叉结构,画出CPU和存储芯片的连接图(见图10—2)。 要求: (1)合理选用下列芯片,门电路自定。 (2)写出每片存储芯片的二进制地址范围。 (3)详细画出存储芯片的片选逻辑。 (4)该存储器在一个存取周期内可向CPU提供多少位信息?

第4题

第5题

A.1

B.2

C.3

D.4

第6题

1 由一个具有8个存储体的低位多体交叉存储体中,如果处理器的访存地址为以下八进制值。求该存储器比单体存储器的平均访问速度提高多少(忽略初启时的延时)? (1)1001,1002,1003,1004, 1005…, 1100 (2)1002,1004,1006,1010, 1012…. 1200 (3)1003,1006,1011,1014, 1017…, 1300

第7题

下列说法不正确的是()。

A.单体多字存储器能提高存储器频宽

B.多体存储器低位交叉编址能提高存储器频宽

C.多体存储器高位交叉编址便于扩大存储器容量

D.多体存储器高位交叉编址能提高存储器频宽

第10题