题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

图2.3.15(a)、(b)所示的逻辑门电路均为+5 V电源供电,在下列两种情况下,分别讨论图2.3.15(a)、(b)的

图2.3.15(a)、(b)所示的逻辑门电路均为+5 V电源供电,在下列两种情况下,分别讨论图2.3.15(a)、(b)的输出各是什么? (1)两个电路均为CMOS门;

1.jpg) (2)两个电路均为74LS系列TTL门,VIL(max)=0.8 V,VIH(min)=2 V。

(2)两个电路均为74LS系列TTL门,VIL(max)=0.8 V,VIH(min)=2 V。

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

图2.3.15(a)、(b)所示的逻辑门电路均为+5 V电源供电,在下列两种情况下,分别讨论图2.3.15(a)、(b)的输出各是什么? (1)两个电路均为CMOS门;

1.jpg) (2)两个电路均为74LS系列TTL门,VIL(max)=0.8 V,VIH(min)=2 V。

(2)两个电路均为74LS系列TTL门,VIL(max)=0.8 V,VIH(min)=2 V。

答案

答案

更多“图2.3.15(a)、(b)所示的逻辑门电路均为+5 V电源供电,在下列两种情况下,分别讨论图2.3.15(a)、(b)的”相关的问题

更多“图2.3.15(a)、(b)所示的逻辑门电路均为+5 V电源供电,在下列两种情况下,分别讨论图2.3.15(a)、(b)的”相关的问题

第2题

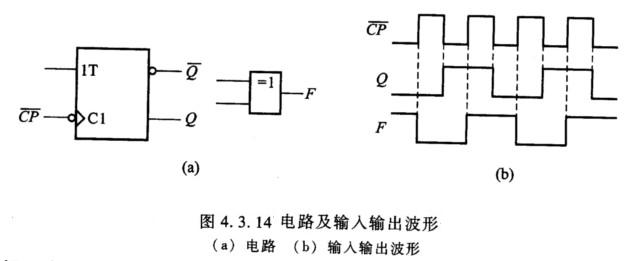

试用图4.3.14(a)给定的触发器和逻辑门设计波形产生电路。要求图(a)中的各信号满足图4.3.14(b)所示时序关系。

第4题

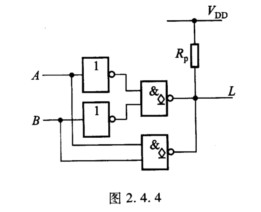

图2.4.4所示为OD门构成的电路。 (1)写出输出端的逻辑表达式; (2)当A、B都为高电平或者都为低电平时,输出何种电平? (3)当A、B有一个为高电平,另一个为低电平时,输出何种电平?

第5题

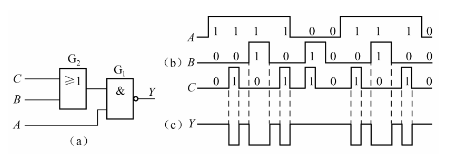

画出图P3.4-1(a),(b)所示门电路的输出波形,其输入波形如图P3.4-1(c)所示。不考虑门的传输延迟时间。写出Y的逻辑表达式并画出真值表。

第6题

图2.3.14(a)、(b)所示为传输门和非门构成的电路及输入波形。试说明该电路实现的逻辑功能,并画出输出L的波形。

第8题

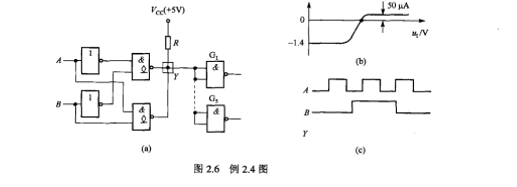

过的最大负载电流ILM≤15mA,输出Y的高、低电平满足UOH≥3V,UOL≤0.4V与非门G1~G5的输入特性如图2.6(b)所示,输入A、B的波形如图2.6(c)所示.

(1)写出函数Y的逻辑表达式.

(2)画出输出Y与输入A、B的对应波形.

(3)计算电阻R的取值范围.

第9题

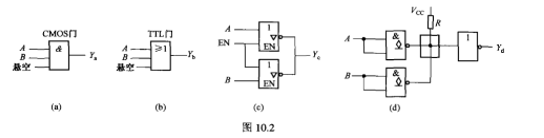

改正下图电路的错误,使其正常工作并得到想要的输出结果:写出图(d)所示TIL门电路的输出Yd的逻辑表达式.

第10题

(1)首先根据图4.4.31对1位数值比较器的行为进行描述,并用Quartus II软件对该模块进行逻辑功能仿真,并给出仿真波形。

(2)然后根据图4.4.32结构,调用上面设计的1位比较器模块和基本门级元件,完成成两位数值比较器的建模。

(3)最后用QuartusII软件对整个电路进行逻辑功能仿真,并给出仿真波形。